Product Summary

The IC41C16256-35TI is a 262,144 x 16-bit high-performance CMOS Dynamic Random Access Memories. The IC41C16256-35TI offers an accelerated cycle access called EDO Page Mode. EDO Page Mode allows 512 random accesses within a single row with access cycle time as short as 10 ns per 16-bit word. The Byte Write control, of upper and lower byte, makes the IC41C16256 ideal for use in 16-, 32-bit wide data bus systems. These features make the IIC41C16256-35TI ideally suited for high-bandwidth graphics, digital signal processing, high-performance computing systems, and peripheral applications.

Parametrics

IC41C16256-35TI absolute maximum ratings: (1)VT Voltage on Any Pin Relative to GND 5V: –1.0 to +7.0 V; (2)VCC Supply Voltage 5V: –1.0 to +7.0 V; (3)IOUT Output Current: 50 mA; (4)PD Power Dissipation: 1 W; (5)TA Commercial Operation Temperature: 0 to +70 ℃; (6)Industrial Operationg Temperature: –40 to +85 ℃; (7)TSTG Storage Temperature: –55 to +125 ℃.

Features

IC41C16256-35TI features: (1)Extended Data-Out (EDO) Page Mode access cycle; (2)TTL compatible inputs and outputs; tristate I/O; (3)Refresh Interval: 512 cycles /8 ms; (4)Refresh Mode: RAS-Only, CAS-before-RAS (CBR), Hidden; (5)Single power supply; (6)5V ±10% (IC41C16256); (7)Byte Write and Byte Read operation via two CAS; (8)Industrail Temperature Range -40℃ to 85℃; (9)Pb-free package is available.

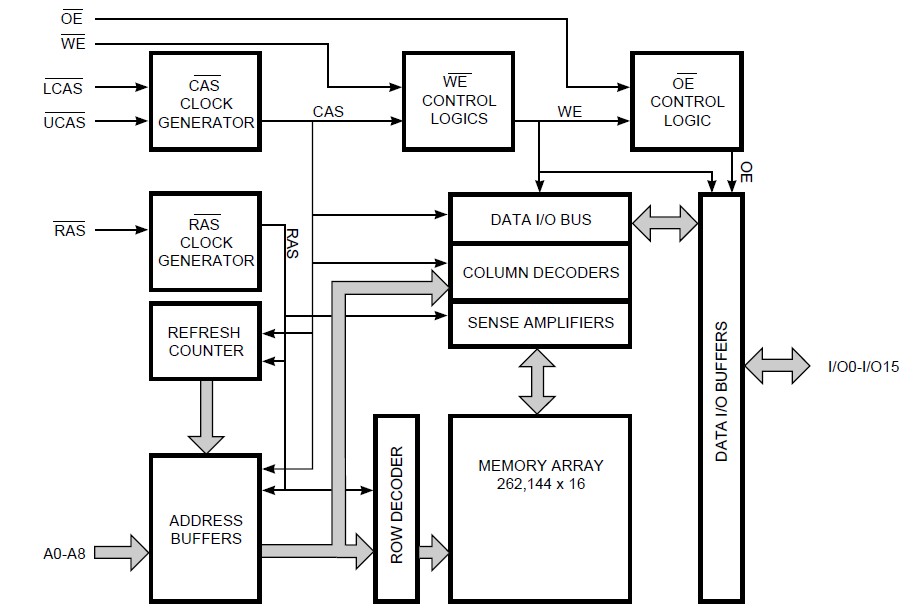

Diagrams

|

IC41SV44054 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

IC41SV44052 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

IC41LV8513 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

IC41LV8512 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

IC41LV82002S |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

IC41LV4405x |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)